Há pouco mais de um ano, a Fundação RISC-V, o grupo que orienta a arquitetura do chip no que na última década se tornou um mercado de processadores ativo e lotado, ratificou a arquitetura do conjunto de instruções básicas (ISA) e especificações relacionadas.

Foi um passo significativo para uma arquitetura relativamente nova fornecida sob licença de código aberto que não exige que as empresas paguem taxas se quiserem construir produtos baseados no ISA ou modificar o próprio ISA e que pretende se estender de microcontroladores a datacenter sistemas.

Os proponentes por trás do RISC-V estão posicionando a arquitetura como uma alternativa ao X86 usado pela Intel e pela AMD que não é aberto e também o Arm, que fornece seus designs de chip para parceiros de fabricação, mas com uma taxa de licenciamento que pode chegar a milhões de dólares.

Um número crescente de empresas - como a Nvidia (que supostamente está considerando fazer uma oferta pela Arm) e a Western Digital - estão começando a abraçar a arquitetura.

Outra empresa que está adotando o RISC-V é o gigante hiperscaler chinês Alibaba. As tensões entre os Estados Unidos e a China sobre a tecnologia estão crescendo e as autoridades chinesas continuam pressionando para que mais dos produtos usados no país sejam cultivados internamente e empresas como Alibaba e SiFive estão adotando a arquitetura RISC-V.

A Alibaba em julho apresentou seu primeiro produto baseado em RISC-V, o XT910 (ou Xuantie 910), um design de 16 núcleos que funciona entre 2,0 GHz e 2,5 GHz gravado em 12 nanômetros processos e que inclui instruções de 16 bits.

A Alibaba afirma que o XT910 é o processador RISC-V mais poderoso até hoje. A empresa falou mais sobre o processador na conferência virtual Hot Chips 2020 desta semana, dando uma visão geral do processador, uma ideia de como ele se compara ao Cortex-A73 da Arm (que é projetado para dispositivos móveis de alto desempenho) e um vislumbre do que a empresa está planejando no futuro. Também nos dá um ponto de referência a partir do qual pensar sobre os processadores de servidor RISC-V.

O chip foi projetado por T-Head, uma jovem unidade de semicondutor operando sob a DAMO Academy do Alibaba. Yu Pu, líder de produto de ponta da T-Head, falou sobre o chip no evento Hot Chips 2020, dizendo que a Alibaba está olhando para RISC-V como base para sua infraestrutura de computação em nuvem e ponta. Pu admitiu que estava no início do desenvolvimento da arquitetura, mas que os engenheiros da empresa estavam confiantes na tecnologia e em como eles podem trabalhar com a comunidade de código aberto para melhorá-la.

"Embora o RISC-V ainda não esteja maduro o suficiente em termos de tecnologia e ecossistema, acreditamos que ele tem um grande potencial", disse ele. "A intenção deste trabalho é contribuir para os núcleos de computação embarcados de alto desempenho e alto desempenho baseados em RISC-V por meio de colaboração de código aberto."

Como muitos fornecedores de componentes de infraestrutura, o Alibaba está olhando para as rápidas mudanças na indústria causadas pelo surgimento da nuvem, mobilidade e Internet das Coisas em termos de enormes quantidades de dados que estão sendo gerados - com projeções de 175 zetabytes até 2025 - e os recursos de computação, rede e armazenamento que serão necessários para executar tecnologias como inteligência artificial (IA), aprendizado de máquina, automação e análise para coletar, armazenar, gerenciar e analisar todos esses dados.

É a IoT cada vez mais inteligente e o "tráfego de computação astronômica" que estão conduzindo a pesquisa por uma infraestrutura de baixo custo e baixo consumo de energia, disse ele.

"O RISC-V é muito atraente neste momento porque, como uma alternativa aos ISAs fechados e caros, o ISA RISC-V aberto e gratuito acelera a inovação do processador por meio da colaboração de padrão aberto", disse Pu. "A escalabilidade, extensibilidade e modularidade permitem aos clientes do processador ... otimização para cargas de trabalho específicas do domínio, como aceleradores de maquinário, processamento de rede, despesas de segurança, controladores de armazenamento e assim por diante, proporcionando grande eficiência de processamento e redução de custos de design. O RISC-V também é muito fácil de acompanhar com outros IPs específicos de domínio de parceiros, tanto do ponto de vista técnico quanto da perspectiva de negócios. RISC-V hoje em dia está se tornando um pouco como ... Unix e sistema operacional Unix. Também é totalmente suportado por nosso AliOS [distribuição Linux do Alibaba]. Como o conjunto de ferramentas está ficando cada vez mais maduro,

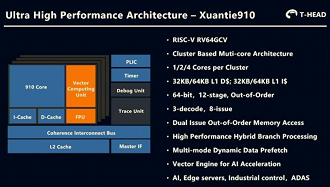

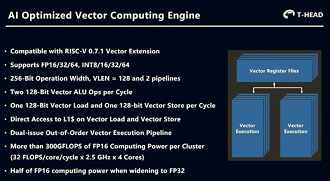

O XT910 é compatível com RISC-V 0.7.1 Vector Extension, inclui um motor vetorial para aceleração de IA e é baseado em processos FinFET de 12 nanômetros da Taiwan Semiconductor Manufacturing Corp. É um projeto multi-core baseado em cluster com até quatro núcleos por cluster e cada núcleo suporta 32 KB a 64 KB de cache de dados L1 e 32 KB a 64 KB de cache de instruções L1. Inclui um preditor de ramificação híbrido, implementando mais de um mecanismo preditor para melhorar o desempenho e a eficiência. O chip também oferece o recurso RISC-V Turbo que usa ajustes como sincronização de múltiplos núcleos e acesso mais rápido à memória para aumentar o desempenho, mas também pode ser desligado para permitir que o chip seja totalmente compatível com outros chips RISC-V.

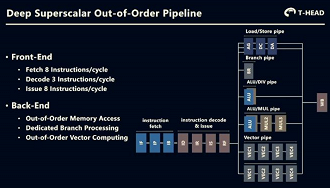

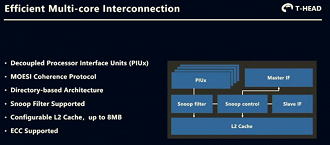

Ele apresenta um pipeline superescalar profundo fora de ordem com oito fetch, três decodificações e oito instruções de emissão por ciclo no front-end e acesso à memória fora de ordem, processamento de ramificação dedicado e computação vetorial fora de ordem no Processo interno. A interconexão de vários núcleos apresenta unidades de interface de processador desacopladas (PIUs), o protocolo de coerência MOESI e um cache L2 configurável de até 8MB.

A IA é a chave para adicionar a inteligência necessária para permitir que os sistemas gerenciem e analisem as grandes quantidades de dados sendo gerados. Abaixo estão os detalhes da extensão de vetor otimizada para AI, que inclui mais de 300GFLops de poder de computação FP16 por cluster.

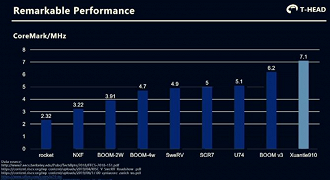

Pu disse que o chip é o processador RISC-V de melhor desempenho no mercado agora, embora ele tenha acrescentado que a SiFive está desenvolvendo seu processador U84, que pode oferecer maior desempenho. No entanto, não há detalhes sobre o U84, então ele não pode ser incluído no gráfico abaixo.

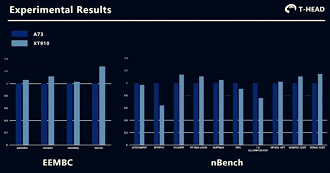

O Alibaba comparou as capacidades do chip com as do Arm Cortex-A73, que é a base da plataforma móvel habilitada para IA Kirin 970 da Huawei que foi introduzida em 2017. Os chips XT910 usados nos testes foram configurados com os mesmos tamanhos de cache L1. Os resultados abaixo mostram o chip Alibaba superando o Cortex-A73 em uma série de parâmetros de benchmark, embora Pu admitisse que o XT910 ainda é um chip jovem e precisa de mais trabalho. Mas os números iniciais são animadores, disse ele.

Ainda não sabemos como o XT910 será implementado. A empresa está usando o chip no Alibaba Cloud e ele pode ser usado com a plataforma Wujian SoC da empresa. Além disso, a empresa planeja disponibilizar a arquitetura do chip para a comunidade de código aberto e está trabalhando com grupos comunitários para atingir esse objetivo, disse Pu.

"A intenção da série Xuantie não é competir com qualquer projeto não-RISC ..., mas sim contribuir para a comunidade RISC-V de código aberto", disse ele.

O chip XT910 também é o primeiro de uma família que a empresa planeja lançar. Pu falou sobre o XT902, um chip de baixa potência na outra extremidade do espectro do XT910 que vem com um Trusted Execution Environment e está na mesma classe de microcontrolador que o Cortex-M0 da Arm.

A empresa também tem três outros em construção - incluindo o XT903, 905, 907 e 908 - que virão com diferentes níveis de desempenho e potência integrados.